? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 中國版Chiplet標(biāo)準(zhǔn)發(fā)布? 或重塑全球半導(dǎo)體產(chǎn)業(yè)鏈

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 2023-01-07? 青野云麓

2023-01-07? 04:12 中國經(jīng)營報官方帳號

本報記者 李玉洋 上海報道

?

在中國首個原生Chiplet(芯粒����,也稱小芯片,是指預(yù)先制造好�����、具有特定功能���、可組合集成的晶片)技術(shù)標(biāo)準(zhǔn)發(fā)布后��,Chiplet概念股迎來一波走強勢頭�。

日前,由中國集成電路領(lǐng)域相關(guān)企業(yè)和專家共同主導(dǎo)制定的《小芯片接口總線技術(shù)要求》團體標(biāo)準(zhǔn)����,正式通過工信部中國電子工業(yè)標(biāo)準(zhǔn)化技術(shù)協(xié)會的審定并發(fā)布。據(jù)悉�����,該技術(shù)標(biāo)準(zhǔn)對中國集成電路產(chǎn)業(yè)延續(xù)“摩爾定律”�,突破先進制程工藝限制具有重要意義。

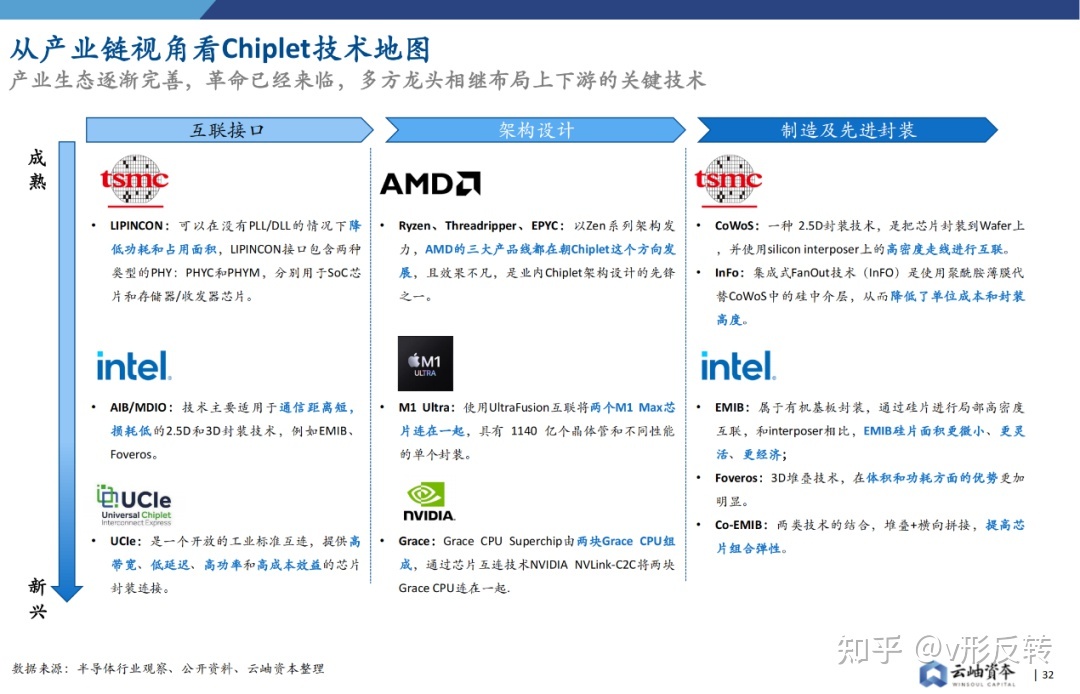

2022年3月�,Intel、AMD����、ARM、高通�、三星、臺積電�、日月光、Google Cloud�、Meta和微軟等巨頭成立Chiplet標(biāo)準(zhǔn)聯(lián)盟,制定了通用Chiplet的高速互聯(lián)標(biāo)準(zhǔn)“Universal Chiplet Interconnect Express”(以下簡稱“UCIe”)���,而中國首個Chiplet技術(shù)標(biāo)準(zhǔn)的發(fā)布���,是因產(chǎn)業(yè)發(fā)展“順勢而為”���。在有了UCIe這樣的國際標(biāo)準(zhǔn)�,中國還需要一套屬于自己的Chiplet技術(shù)標(biāo)準(zhǔn)嗎?

對此��,作為小芯片標(biāo)準(zhǔn)的主要發(fā)起人和起草人,中國計算機互連技術(shù)聯(lián)盟(CCITA)秘書長郝沁汾表示����,在國內(nèi)研發(fā)先進制程受到客觀影響的大背景下,企業(yè)對于屬于中國的Chiplet技術(shù)標(biāo)準(zhǔn)的訴求是比較強烈的����,很多國內(nèi)廠商都希望去應(yīng)用Chiplet技術(shù)�,也希望國內(nèi)推動這一技術(shù)的標(biāo)準(zhǔn)化。

而芯謀研究總監(jiān)王笑龍告訴《中國經(jīng)營報》記者:“政治干預(yù)經(jīng)濟����,美國要孤立中國,中國當(dāng)然要有自己的標(biāo)準(zhǔn)���,沒辦法完全看國際標(biāo)準(zhǔn)����。”電子創(chuàng)新網(wǎng)CEO張國斌也認(rèn)為����,中國版Chiplet技術(shù)標(biāo)準(zhǔn)的發(fā)布具有兩重意義,一是防止標(biāo)準(zhǔn)被政治因素影響�����,二是以這個標(biāo)準(zhǔn)為基礎(chǔ)��,打造中國的Chiplet產(chǎn)業(yè)體系����。

需有中國版的Chiplet技術(shù)標(biāo)準(zhǔn)

時間退回到2020年8月,中科院計算所牽頭成立了中國計算機互連技術(shù)聯(lián)盟���,重點圍繞Chiplet小芯片和微電子芯片光I/O(輸入/輸出)成立了兩個標(biāo)準(zhǔn)工作組���,就前者而言,CCITA于2021年5月在工信部立項了Chiplet標(biāo)準(zhǔn)��,即《小芯片接口總線技術(shù)要求》,由中科院計算所�����、工信部電子四院和國內(nèi)多個芯片廠商合作展開標(biāo)準(zhǔn)制定工作���。小芯片接口標(biāo)準(zhǔn)制定集結(jié)了國內(nèi)產(chǎn)業(yè)鏈上下游60多家單位共同參與研究�。

據(jù)了解���,中國自建的Chiplet技術(shù)標(biāo)準(zhǔn)描述了CPU��、GPU�、人工智能芯片��、網(wǎng)絡(luò)處理器和網(wǎng)絡(luò)交換芯片等應(yīng)用場景的小芯片接口總線技術(shù)要求�����,包括總體概述��、接口要求��、鏈路層�、適配層、物理層和封裝要求等����,以靈活應(yīng)對不同的應(yīng)用場景、適配不同能力的技術(shù)供應(yīng)商�,通過對鏈路層、適配層�����、物理層的詳細(xì)定義�,實現(xiàn)在小芯片之間的互連互通,并兼顧了PCIe(一種高速串行計算機擴展總線標(biāo)準(zhǔn))等現(xiàn)有協(xié)議的支持�,列出了對封裝方式的要求。

“Chiplet是大勢所趨�,隨著摩爾定律逐漸放緩,需要高級封裝技術(shù)繼續(xù)提升芯片或者模組的晶體管密度����。”張國斌表示�,UCIe主要是由幾家國際大廠來主導(dǎo),中國廠商扮演跟隨角色�����,“要推必須是代工廠、封測廠�����、芯片設(shè)計企業(yè)一起搞”����。對此,半導(dǎo)體行業(yè)資深觀察人士王如晨觀點更為直接���,他認(rèn)為UCIe對相關(guān)中國企業(yè)明顯有排他性�。

截至目前�,基于Chiplet架構(gòu)進行芯片設(shè)計,但由于技術(shù)門檻較高�,如果只靠自身完成全部設(shè)計,需要芯片廠商具備從芯片整體的架構(gòu)設(shè)計到其中并行或者串行物理層接口�,甚至先進封裝的能力,當(dāng)下只有Intel公司能做到����;因此,在我國首先需形成完整的�����、面向Chiplet架構(gòu)設(shè)計芯片的社會分工���,在此基礎(chǔ)上��,形成Chiplet標(biāo)準(zhǔn)則更加重要����。

王笑龍表示:“在目前形勢下���,美國不想帶中國玩���,所以說Chiplet我們肯定要搞,在參考國際標(biāo)準(zhǔn)的基礎(chǔ)上���,我們也要提自己的一些東西���,獨立自主加上盡可能國際合作的雙結(jié)合?���!?/span>

郝沁汾也持有類似觀點。他表示,中國小芯片標(biāo)準(zhǔn)更偏重本土化的需求��,與UCIe并不是競爭關(guān)系��,目前CCITA已經(jīng)在考慮和Intel UCIe在物理層上兼容�,以降低IP廠商支持多種Chiplet標(biāo)準(zhǔn)的成本。

“我們自己制定Chiplet標(biāo)準(zhǔn)���,除了參照企業(yè)的設(shè)計研發(fā)能力外����,還要切實參考國內(nèi)的生產(chǎn)制造的能力��?!蓖跣堁a充說。

規(guī)?�;涞厥翘魬?zhàn)

在王如晨看來�,中國推出自己的Chiplet技術(shù)標(biāo)準(zhǔn)時間緊迫,“這個動作對中國來說更現(xiàn)實���,我們不僅遭受摩爾定律困擾��,還遭受鉗制”��。

他認(rèn)為���,在成熟的工藝區(qū)間,尤其14納米或再進一步的節(jié)點�����,如果全產(chǎn)業(yè)鏈協(xié)同一體�����,反而能化解很多挑戰(zhàn)��,并能驅(qū)動上游被鉗制的環(huán)節(jié)進步���?����!爸袊@方面確實也有自己的差異化優(yōu)勢�,一是產(chǎn)業(yè)鏈完整��,二是市場因素����。大國體量或者巨型市場的好處����,就是一旦縱橫兩個維度協(xié)同起來�,一個領(lǐng)域很容易上規(guī)模。這就可能會與美國脅迫的同類聯(lián)盟����,形成兩大生態(tài),也是芯片行業(yè)的兩種商業(yè)��、供應(yīng)鏈操作系統(tǒng)��?����!?/span>

言下之意��,中國制定自己的Chiplet技術(shù)標(biāo)準(zhǔn)���,通過成熟制程實現(xiàn)Chiplet的堆疊封裝能從一定程度緩解對先進制程的依賴���,特別是在中美科技爭端持續(xù)的背景下�。然而����,難點也有不少。

“一是雖然由官方主導(dǎo)���,但市場化要素會有自己的考量,畢竟有些企業(yè)所在賽道沒被鉗制�,或者受影響較小,積極性不夠��,未來利益不均����;二是Chiplet這個領(lǐng)域還是有技術(shù)挑戰(zhàn)的,不可能只停留在成熟工藝����,畢竟各家所處領(lǐng)域、應(yīng)用場景不同�,消費互聯(lián)網(wǎng)和工業(yè)互聯(lián)網(wǎng)以及更多場景的產(chǎn)品與技術(shù)訴求不統(tǒng)一,前者演進要更快�。”王如晨說����。

他還表示���,大部分企業(yè)通常能突破部分供應(yīng)鏈鉗制,長期看中國真正遭受壓力的���,其實是產(chǎn)業(yè)互聯(lián)網(wǎng)����、數(shù)字基礎(chǔ)設(shè)施以及相關(guān)場景�����?���!懊绹驌舻闹饕侵袊I(yè)數(shù)字支撐力,尤其產(chǎn)業(yè)互聯(lián)網(wǎng)��、AI底層等要素����,很多口實落在軍事、軍民兩用等上面�?���!蓖跞绯空f����。

隨著國內(nèi)首個原生Chiplet技術(shù)標(biāo)準(zhǔn)發(fā)布,不少上市公司借機向外界釋放量產(chǎn)消息����,Chiplet概念股持續(xù)走強。對此��,王如晨表示:“炒作也正常�����,芯片行業(yè)近幾年來一直在炒作�,關(guān)鍵還是看能不能落地��,真能落地的話���,還是會有一定聲量��。畢竟有市場因素��,一旦上規(guī)模����,就能形成事實性的行業(yè)標(biāo)準(zhǔn),以中國在全球供應(yīng)鏈中的地位�,尤其是制造業(yè)、終端���、中間產(chǎn)品的競爭力�����,輻射海外����,也會有自己的一定地盤��?���!?/span>

他指出,現(xiàn)在的供應(yīng)鏈乃至產(chǎn)業(yè)競爭����,很少是單一企業(yè)的競爭�����,而呈現(xiàn)為聯(lián)盟����、生態(tài)之間的競爭����。Chiplet技術(shù)標(biāo)準(zhǔn)雖然已經(jīng)發(fā)布,但切忌內(nèi)卷�����、內(nèi)耗和反復(fù)妥協(xié)���。

“如果沒有熱情,只是狹義的半導(dǎo)體公司����、官方機構(gòu),即便有幾家系統(tǒng)或終端企業(yè)(手機���、PC���、家電或物聯(lián)網(wǎng)企業(yè))參與��,還是很難發(fā)展好�,得有基礎(chǔ)設(shè)施類企業(yè)才能產(chǎn)生更大的協(xié)同��?��!蓖跞绯勘硎?�,沒有基礎(chǔ)類公司參與��,Chiplet也很難規(guī)?;?����,BAT���、京東���、抖音、拼多多背后對半導(dǎo)體的需求很大,且更能匹配成熟工藝���。

“2013年�,臺積電創(chuàng)始人張忠謀就說���,未來影響全球半導(dǎo)體行業(yè)的公司�,會有華為��、阿里巴巴這些類型的企業(yè)����,華為是一個維度,阿里巴巴是另一個維度����。”王如晨表示�。

《Chiplet生逢其時,中國半導(dǎo)體企業(yè)如何借此破局��?|芯片行業(yè)觀察》

2022-08-02? 10:43? 張通社? 上海

編者按:

作為半導(dǎo)體EDA領(lǐng)域新秀企業(yè)之一的瞬曜EDA近日與張通社聯(lián)合打造了“芯片行業(yè)觀察”欄目�����,通過結(jié)合媒體人與芯片行業(yè)從業(yè)者的認(rèn)知與觀點�����,旨在分享半導(dǎo)體行業(yè)現(xiàn)狀與趨勢��,以饗讀者�,歡迎留言交流。

?

近年來��,關(guān)于“摩爾定律”即將走向終結(jié)的觀點大行其道����,“后摩爾時代”已成為業(yè)內(nèi)一大熱詞。隨之而來的問題是�,如何在現(xiàn)有的工藝制程下,既能繼續(xù)提升芯片的性能���,又能保持成本不變或降低����?

處于風(fēng)口當(dāng)中的Chiplet技術(shù)����,正被不少業(yè)內(nèi)人士視為摩爾定律放緩之后���、中國半導(dǎo)體企業(yè)彎道超車的機會。尤其是華為被美國制裁�、先進芯片受制之后,Chiplet備受市場關(guān)注�。據(jù)Omdia報告,到2024年��,Chiplet的市場規(guī)模將達(dá)到58億美元��,2035年則超過570億美元�����,Chiplet的全球市場規(guī)模將迎來快速增長��。

?

事實上����,Chiplet并非是一個新的概念,其概念最早源于1970年代誕生的多芯片模組����,即由多個同質(zhì)或異質(zhì)的較小芯片組成大芯片,也就是從原來設(shè)計在同一個SoC中的芯片��,被分拆成許多不同的小芯片分開制造再加以封裝或組裝�,故稱此分拆之芯片為“小芯片”(Chiplet)。

2015年��,Marvell創(chuàng)始人周秀文博士在ISSCC 2015上提出MoChi(Modular Chip����,模塊化芯片)概念,這是Chiplet最早的雛形��。近年來����,這個概念開花結(jié)果,AMD��、英特爾�����、臺積電���、英偉達(dá)等國際芯片巨頭均開始紛紛入局Chiplet����。同時,隨著入局的企業(yè)越來越多��,設(shè)計樣本也越來越多���,開發(fā)成本也開始下降�����,大大加速了Chiplet生態(tài)發(fā)展���。

01.Chiplet:延續(xù)摩爾定律的新法寶

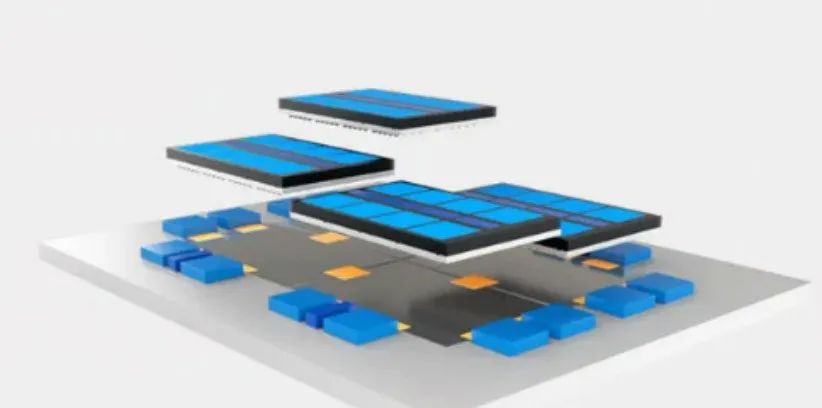

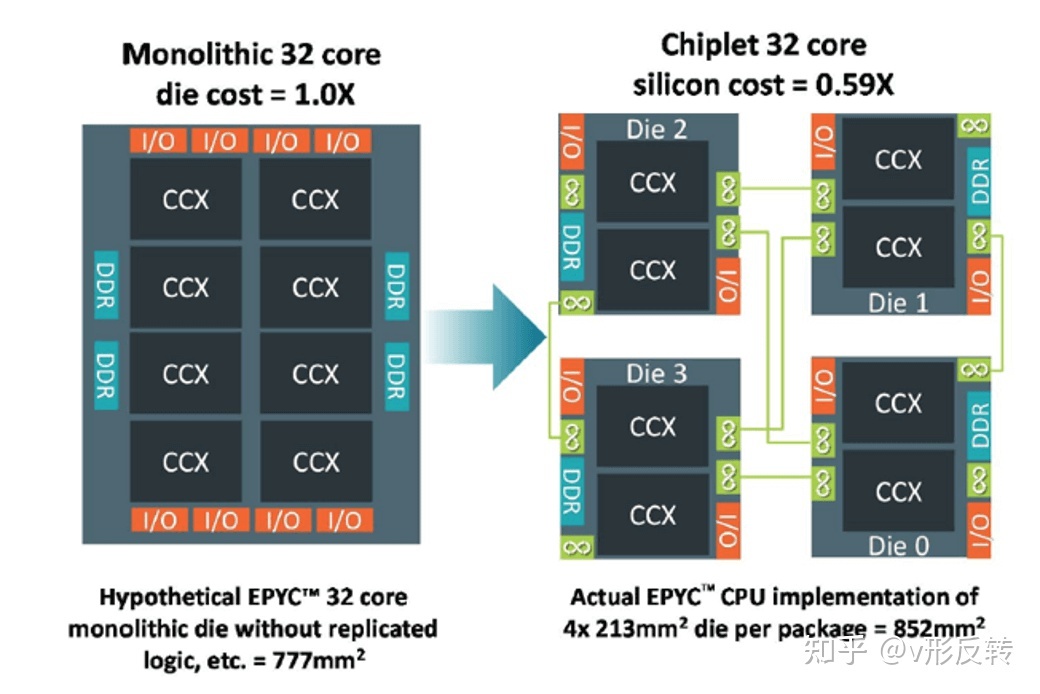

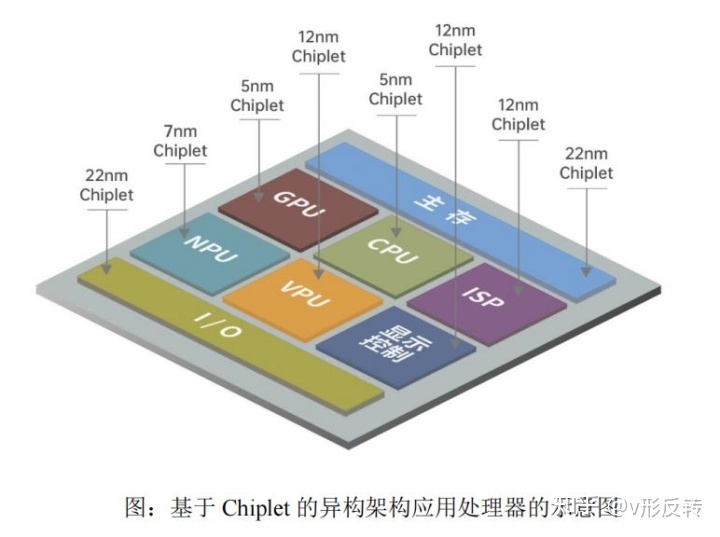

目前,主流系統(tǒng)級單芯片(SoC)都是將多個負(fù)責(zé)不同類型計算任務(wù)的計算單元���,通過光刻的形式制作到同一塊晶圓上���。作為先進封裝技術(shù)的代表,Chiplet走向了和傳統(tǒng)SoC完全不同的道路�。它將復(fù)雜芯片拆解成一組具有單獨功能的小芯片單元die(裸片),通過die-to-die將模塊芯片和底層基礎(chǔ)芯片封裝組合在一起�,類似于搭建樂高積木,形成一個系統(tǒng)芯片����,以實現(xiàn)一種新形式的IP復(fù)用����。

?

Chiplet技術(shù)的發(fā)展和興起��,既是技術(shù)發(fā)展需要��,也是經(jīng)濟規(guī)律的驅(qū)動����。如今單品出貨上億的手機SoC研發(fā)成本往往達(dá)到10億美元以上���,而物聯(lián)網(wǎng)細(xì)分領(lǐng)域的出貨和利潤難以覆蓋這樣的研發(fā)投入���。為此,芯片行業(yè)正在積極探索在單個封裝里實現(xiàn)分解SoC��、多芯片異構(gòu)集成的Chiplet技術(shù)�,來平衡這種研發(fā)投入上升和出貨量下降之間的矛盾。

從其技術(shù)特點和當(dāng)前進展綜合來看�����,Chiplet的優(yōu)勢主要歸結(jié)為幾個方面:首先�����,Chiplet可以大幅提高大型芯片的良率。目前在高性能計算�、AI等方面的巨大運算需求,推動了邏輯芯片內(nèi)的運算核心數(shù)量快速上升����,同時配套的SRAM容量、I/O數(shù)量也在大幅提升���,整個芯片晶體管數(shù)量暴漲�。而通過Chiplet設(shè)計���,可將超大型的芯片按照不同的功能模塊切割成獨立的小芯片���,進行分開制造,既能有效改善良率�,也能夠降低因不良率導(dǎo)致的成本。

其次����,Chiplet可以降低設(shè)計的復(fù)雜度和設(shè)計成本。若在芯片設(shè)計階段,就將大規(guī)模的SoC按照不同的功能模塊分解為一個個的芯粒���,那么部分芯?���?梢宰龅筋愃颇K化的設(shè)計��,而且可以重復(fù)運用在不同的芯片產(chǎn)品當(dāng)中���。這樣可以大幅降低芯片設(shè)計的難度和設(shè)計成本,同時也有利于后續(xù)產(chǎn)品的迭代���,加速產(chǎn)品的上市周期����。

此外�,Chiplet還能降低芯片制造的成本。將SoC進行Chiplet化之后��,不同的芯?����?梢愿鶕?jù)需要來選擇合適的工藝制程分開制造����,然后再通過先進封裝技術(shù)進行組裝�,不需要全部都采用先進的制程在一塊晶圓上進行一體化制造����,這樣可以極大的降低芯片的制造成本。

盡管優(yōu)勢突出�,并不是所有芯片都適合使用Chiplet,不少情況下單顆集成的系統(tǒng)芯片會更有價值����。相較之下,AI芯片對于芯片的設(shè)計規(guī)模要求最高�����,且需整合高頻寬記憶體��,高速I/O���、高速網(wǎng)絡(luò)等模組�。Chiplet架構(gòu)一般采用3D集成方案��,減小了芯片面積,擴展了空間�,是對AI芯片最佳、最具經(jīng)濟效益的設(shè)計����。

此外,國內(nèi)半導(dǎo)體創(chuàng)業(yè)企業(yè)中做CPU���、GPU等“大芯片”的企業(yè)越來越多��,隨著功能集成要求更多����,性能要求更高����,設(shè)計面臨的挑戰(zhàn)也越來越大�,Chiplet則可以實現(xiàn)不同功能模塊的區(qū)隔,根據(jù)各自的最優(yōu)迭代節(jié)奏分階段演進��,有效降低研發(fā)難度�。

Chiplet也非常適合汽車自動駕駛芯片。由于汽車自動駕駛芯片對于算力要求非常高����,芯片的面積很大�,成本很高�����,車規(guī)級的認(rèn)證周期又很長��,采用Chiplet設(shè)計���,不僅可以降低設(shè)計難度�����、提升良率���、降低設(shè)計和制造成本,更為關(guān)鍵的是還能夠提供更高的安全性和快速迭代���。

在數(shù)字經(jīng)濟趨勢下����,各種超大算力芯片將有望率先采用基于Chiplet的設(shè)計實現(xiàn)思路和工程實踐方法�。高性能服務(wù)器/數(shù)據(jù)中心����、自動駕駛�、筆記本/臺式電腦、高端智能手機等將在未來幾年成為Chiplet的主要應(yīng)用場景���,引領(lǐng)該市場增長�����。

02.UCIe:Chiplet 互聯(lián)標(biāo)準(zhǔn)的關(guān)鍵一步

盡管有諸多優(yōu)勢加持��,但Chiplet也面臨不少挑戰(zhàn)�。受限于不同架構(gòu)���、不同制造商生產(chǎn)的die之間的互連接口和協(xié)議的不同����,設(shè)計者必須考慮到工藝制程�����、封裝技術(shù)�����、系統(tǒng)集成���、擴展等諸多復(fù)雜因素�����。同時還要滿足不同領(lǐng)域�、不同場景對信息傳輸速度���、功耗等方面的要求����,使得Chiplet的設(shè)計過程異常艱難���,而解決這些問題的最大挑戰(zhàn)就是缺少統(tǒng)一的互連標(biāo)準(zhǔn)協(xié)議�����。

此外��,隨著Chiplet逐步發(fā)展���,未來來自不同廠商的芯粒之間的互聯(lián)需求必然會爆發(fā)�。因此��,在技術(shù)成熟和形成商業(yè)潮流之前���,行業(yè)廠商需要搭起一座Chiplet互聯(lián)接口標(biāo)準(zhǔn)化的“橋梁”�。

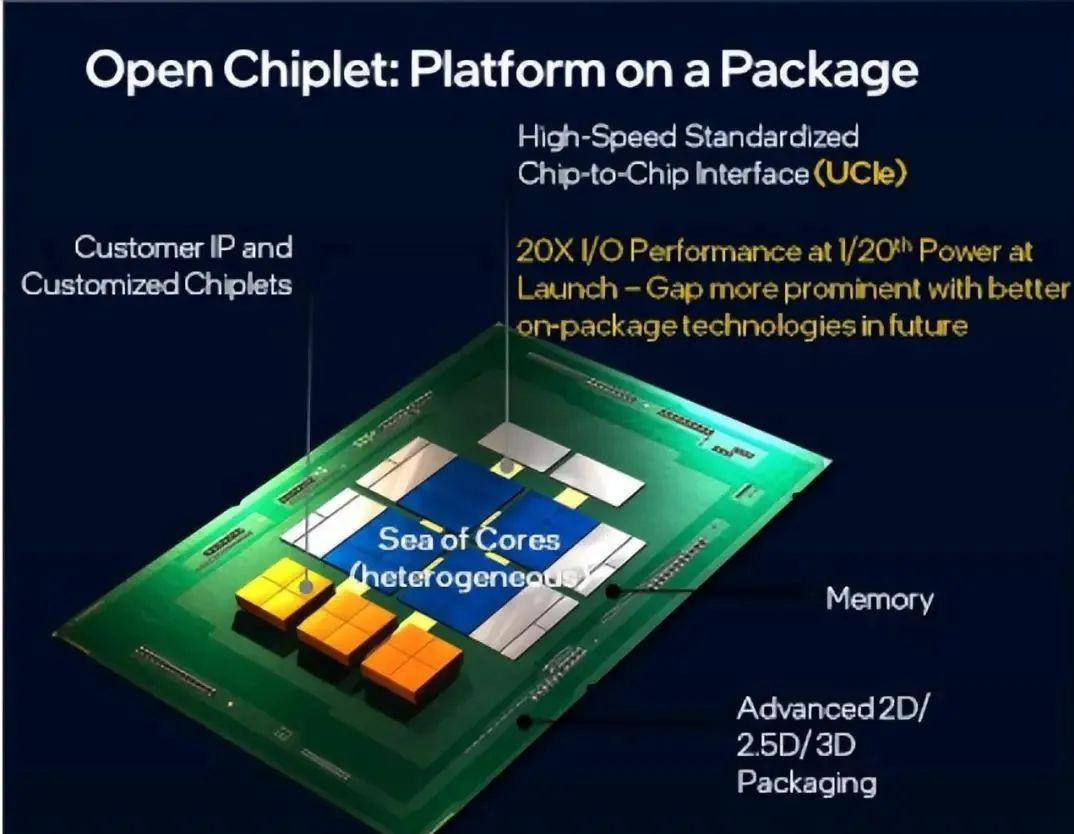

今年3月�����,AMD�、Arm、英特爾���、高通����、三星����、臺積電���、微軟�、谷歌、Meta�����、日月光十家半導(dǎo)體產(chǎn)業(yè)上下游企業(yè)組成UCIe(Universal Chiplet Interconnect Express)產(chǎn)業(yè)聯(lián)盟��。對于半導(dǎo)體行業(yè)來說�,眾星捧月般的UCIe問世,意味著一個可以推廣普及的Chiplet 標(biāo)準(zhǔn)來了���!

?

作為一個由諸多半導(dǎo)體����、科技巨頭所建立的組織���,UCIe產(chǎn)業(yè)聯(lián)盟已經(jīng)推出UCIe 1.0標(biāo)準(zhǔn)��,UCIe 1.0標(biāo)準(zhǔn)是針對Chiplet技術(shù)建立的����,它定義了封裝內(nèi)Chiplet之間的互連�,以實現(xiàn)Chiplet在封裝級別的普遍互連和開放的Chiplet生態(tài)系統(tǒng)���。

該標(biāo)準(zhǔn)是一個三層協(xié)議,物理層負(fù)責(zé)電信號�����、時鐘��、鏈路協(xié)商�����、邊帶等��,裸片適配層(Die-to-Die Adapter)為芯粒提供鏈路狀態(tài)管理和參數(shù)協(xié)商����,它可選地通過循環(huán)冗余校驗 (CRC)和重傳機制保證數(shù)據(jù)的可靠傳輸,UCIe接口通過這兩層與標(biāo)準(zhǔn)互連協(xié)議層相連����。

?

此前,各廠商實現(xiàn)芯粒封裝均采用獨家定制技術(shù)��,這給芯粒技術(shù)進一步普及帶來了很高的成本和阻力,UCIe接口技術(shù)標(biāo)準(zhǔn)化以后�,讓終端使用者打造SoC芯片時���,可以自由搭配來自多個廠商生態(tài)系統(tǒng)中的小芯片零件����,這將加速推動開放的Chiplet平臺發(fā)展�����,并橫跨x86�����、Arm�、RISC-V等架構(gòu)和指令集。

值得注意的是��,一個月后�����,芯原微電子��、超摩科技、芯和半導(dǎo)體�、芯耀輝等中國大陸半導(dǎo)體企業(yè)相繼宣布加入該聯(lián)盟,UCIe迎來了首批中國軍團����。截至目前,摩爾精英���、燦芯半導(dǎo)體�、憶芯科技�、芯耀輝、牛芯半導(dǎo)體�����、芯云凌����、長鑫存儲、超摩科技��、希姆計算�、世芯電子、阿里巴巴�����、OPPO、愛普科技��、芯動科技���、藍(lán)洋智能等多家國內(nèi)企業(yè)已成為UCIe聯(lián)盟成員,為發(fā)力Chiplet的中國半導(dǎo)體產(chǎn)業(yè)注入了一針強心劑�����。

03.多路并進,助推Chiplet技術(shù)在國內(nèi)發(fā)展

對于中國半導(dǎo)體而言��,Chiplet被視為中國與國外差距相對較小的先進封裝技術(shù)�����,有望帶領(lǐng)中國半導(dǎo)體產(chǎn)業(yè)在后摩爾時代實現(xiàn)質(zhì)的突破����。中國企業(yè)亦在Chiplet上有所作為,積極融入UCIe生態(tài)�,走向Chiplet研發(fā)的道路。

華為海思是國內(nèi)最早嘗試Chiplet的廠商之一���。2014年����,華為海思與臺積電合作的64位Arm架構(gòu)服務(wù)器處理器Hi16xx,采用臺積電異構(gòu)CoWoS 3D IC封裝工藝���,將16nm邏輯芯片與28nm I/O芯片集成在一起�����,實現(xiàn)了具有成本效益的系統(tǒng)解決方案�����,可以視為早期Chiplet實踐���。

除華為之外,國內(nèi)其他諸多半導(dǎo)體公司也有了驚喜的進步�����。如芯原股份有望是業(yè)內(nèi)首批推出商用Chiplet的公司�����,近年來一直致力于Chiplet技術(shù)和產(chǎn)業(yè)的推進?;凇癐P芯片化,IP as a Chiplet”和“芯片平臺化���,Chiplet as a Platform”兩大設(shè)計理念�����,芯原推出了基于Chiplet架構(gòu)所設(shè)計的高端應(yīng)用處理器平臺����,目前該平臺12nm SoC版本已完成流片和驗證�����,正在進行Chiplet版本的迭代��。

在Chiplet領(lǐng)域已耕耘多年的芯動科技���,推出的首款高性能服務(wù)器級顯卡GPU“風(fēng)華1號”就使用了Innolink Chiplet技術(shù),將不同功能不同工藝制造的Chiplet進行模塊化封裝���,成為一個異構(gòu)集成芯片����。2022年4月,它又率先推出國產(chǎn)自主研發(fā)物理層兼容UCIe標(biāo)準(zhǔn)的IP解決方案——Innolink Chiplet��。據(jù)悉��,這是國內(nèi)首套跨工藝��、跨封裝的Chiplet(芯粒)連接解決方案���,且已在先進工藝上量產(chǎn)驗證成功���。

?

寒武紀(jì)在2021年11月發(fā)布了其第三代云端AI芯片思元370,基于7nm制程并且是其首款基于Chiplet技術(shù)的AI芯片��,在一顆芯片中封裝2顆AI計算芯粒(MLU-Die)�,每一個MLU-Die具備獨立的AI計算單元、內(nèi)存��、IO以及MLU-Fabric控制和接口���,通過MLU-Fabric保證兩個MLU-Die間的高速通訊��,可以通過不同MLU-Die組合規(guī)格多樣化的產(chǎn)品�����,實現(xiàn)不同算力�����、內(nèi)存和編解碼器的組合���。

摩爾精英也在探索建立一個SiP的平臺����,通過嚴(yán)選的SiP芯片��、借力現(xiàn)有的KGD裸片過渡��,統(tǒng)一芯片生產(chǎn)和品質(zhì)控制�,建立一站式Chiplet研發(fā)�、生產(chǎn)、銷售協(xié)作平臺�����,從而能讓更多的芯片企業(yè)享受到SiP設(shè)計和柔性生產(chǎn)的服務(wù)���。

除了上述廠商�,相繼宣布加入UCIe聯(lián)盟的超摩科技、芯耀輝等公司��,以及正在默默采用Chiplet技術(shù)攻堅的諸多高性能CPU����、GPU和大型AI芯片初創(chuàng)公司等,國內(nèi)芯片設(shè)計����、應(yīng)用產(chǎn)業(yè)鏈都積極參與到全球Chiplet生態(tài)系統(tǒng)中一起協(xié)作,為相關(guān)行業(yè)技術(shù)規(guī)范��、標(biāo)準(zhǔn)的完善添磚加瓦�。

04.Chiplet潮流下的危與機

雖然Chiplet正展現(xiàn)出諸多好處和市場潛力,但是要充分發(fā)揮其效力��,仍面臨著一些需要解決的難題和挑戰(zhàn)�����。

其中����,解決互聯(lián)標(biāo)準(zhǔn)只是第一步�,要將Chiplet真正結(jié)合在一起���,最終還要依靠先進封裝���。目前臺積電擁有CoWoS/InFO、英特爾擁有EMIB�、Fovores 3D等,Chiplet使用的先進封裝多種多樣�,而UCIe1.0標(biāo)準(zhǔn)沒有涵蓋用于在小芯片之間提供物理鏈接的封裝/橋接技術(shù)。未來隨著Chiplet 技術(shù)的發(fā)展終究會使小芯片間的互聯(lián)達(dá)到更高的密度����,要應(yīng)對先進封裝功能和密度的不斷提升,散熱����、應(yīng)力和信號傳輸?shù)榷际侵卮蟮目简灐?/span>

對于芯片設(shè)計來說,雖然依托Chiplet無需再去設(shè)計復(fù)雜的大芯片��,但是將SoC分解Chiplet化��,并將其整合到一個2.5D/3D封裝當(dāng)中�����,會帶來系統(tǒng)復(fù)雜度的大幅提升����,在系統(tǒng)設(shè)計方面存在較大挑戰(zhàn)。

芯片測試層面��,將一顆大的SoC芯片拆分成多個芯粒����,相較于測試完整芯片難度更大,尤其是當(dāng)測試某些并不具備獨立功能的Chiplet 時�����,測試程序更為復(fù)雜���。同時���,為了提升合封后的整體良率,Chiplet集成也對測試和質(zhì)量管控提出了更高的要求�����,此外也對晶圓級CP與Chiplet合封后成品FT測試流程和測試設(shè)備提出更高挑戰(zhàn)。

除了芯片設(shè)計�����、驗證�����、封裝與測試以外���,支持Chiplet芯片設(shè)計的EDA工具鏈以及生態(tài)是否完善��,是否可持續(xù)發(fā)展�,也是Chiplet技術(shù)成功所需要解決的關(guān)鍵問題���。Chiplet技術(shù)需要EDA工具從架構(gòu)探索���、芯片設(shè)計、物理及封裝實現(xiàn)等提供全面支持����,以在各個流程提供智能、優(yōu)化的輔助���,避免人為引入問題和錯誤�。

UCIe 1.0在很大程度上是一個“起始”標(biāo)準(zhǔn)����,本質(zhì)上只定義了2D和2.5D芯片封裝,而沒有3D直接die-to-die技術(shù)(如即將推出的fooveros direct)����。隨著3D芯片封裝的出現(xiàn),Chiplet理念下不同die的堆疊����,同樣將面臨可靠性、信號完整性�����、電源完整性���、熱分析等一系列仿真分析驗證問題���,需要EDA與芯片設(shè)計廠商攜手破解。

針對于此�����,芯和半導(dǎo)體早在去年年底已全球首發(fā)了“3DIC先進封裝設(shè)計分析全流程”EDA平臺,是業(yè)界首個用于3DIC多芯片系統(tǒng)設(shè)計分析的統(tǒng)一平臺����,為用戶構(gòu)建了一個完全集成、性能卓著且易于使用的環(huán)境�,提供了從開發(fā)、設(shè)計�、驗證、信號完整性仿真��、電源完整性仿真到最終簽核的3DIC全流程解決方案����,全面支持2.5D Interposer、3DIC和Chiplet設(shè)計����。

成立于2021年4月的中國EDA創(chuàng)新“黑馬”瞬曜 EDA,不僅在數(shù)字驗證領(lǐng)域���,用“中國高鐵”的方式��,填補了數(shù)字芯片驗證在目前市場上的技術(shù)空白���,并在成立不到一年的時間內(nèi)就獲得了客戶訂單��,得到了客戶的積極認(rèn)可與肯定。

在日前舉辦的CCF Chip 2022大會上����,公司創(chuàng)始人傅勇在國產(chǎn)數(shù)字EDA工具鏈技術(shù)論壇上,分析了Chiplet設(shè)計方法學(xué)對數(shù)字驗證的新挑戰(zhàn)���,并介紹了瞬曜為解決系統(tǒng)級高速驗證和仿真方面的需求所做的努力�。

目前�����,瞬曜EDA推出了RTL高速仿真器ShunSim���,該高速仿真器可以實現(xiàn)對百億門超大規(guī)模集成電路的仿真驗證��,效率較市面上的傳統(tǒng)仿真器高出10-100倍���,產(chǎn)品內(nèi)置經(jīng)過了大量商用案例驗證的穩(wěn)健安全的仿真內(nèi)核Verilator,具備商業(yè)廣闊前景和持續(xù)迭代能力��。

?

據(jù)傅勇介紹,ShunSim采用了智能編譯分割技術(shù)���,能夠?qū)⒃九茉谝粋€ CPU 上的設(shè)計����,分割成好幾個小的模塊進行�����,這使 ShunSim 能夠充分發(fā)揮多服務(wù)器多核并行算力����,十分適合Chiplet芯片設(shè)計。

同時�,為完善驗證方案,增強芯片驗證效率����,瞬曜開發(fā)了全新一代系統(tǒng)級驗證方案YAOVIP,幫助芯片設(shè)計師更快���、更準(zhǔn)確的定位和發(fā)現(xiàn)問題�����。由此��,瞬曜EDA基于這兩大產(chǎn)品線構(gòu)建的平臺級芯片驗證解決方案���,可為Chiplet等關(guān)鍵芯片設(shè)計�����,提供專業(yè)的數(shù)字驗證方案和服務(wù)支持。

“作為SoC的后繼者����,Chiplet對于國產(chǎn)半導(dǎo)體行業(yè)是一個很好的發(fā)展機遇。作為EDA廠商����,瞬曜非常希望有機會與各IP廠商、高校���、研究所合作����,切實拿出不一樣的技術(shù)方案��。”誠如傅勇所言��,Chiplet新型設(shè)計技術(shù)的出現(xiàn)���,對國內(nèi)集成電路產(chǎn)業(yè)無疑是后來居上的有利契機��,而UCIe 1.0標(biāo)準(zhǔn)的推出���,將會打通芯粒跨廠商互聯(lián)的最后一道屏障����,助力半導(dǎo)體產(chǎn)業(yè)的發(fā)展。

但Chiplet模式的發(fā)展還有很長的路要走�����,它既是一次技術(shù)升級��,包括封裝測試技術(shù)���、EDA工具����、芯片架構(gòu)設(shè)計等,也可能帶來一次對傳統(tǒng)半導(dǎo)體產(chǎn)業(yè)鏈的重構(gòu)�����。面對接下來的Chiplet在全球市場上的井噴式增長��,中國半導(dǎo)體企業(yè)踏上風(fēng)口卻仍需努力���,通力合作��,拿出一流的Chiplet產(chǎn)品,方能提升我國半導(dǎo)體在高性能芯片上的生產(chǎn)能力���,站上后摩爾時代的大舞臺���。

《一文弄懂Chiplet及概念股》

2022-08-07? 14:34? ?v形大反轉(zhuǎn)? 廣東

風(fēng)險提示:本文內(nèi)容參考各研究所相關(guān)研報及公開資料(詳見附錄),不代表本人觀點�,也不構(gòu)成任何投資建議。您看過本文后做出的任何投資決策與本人無關(guān)�,市場有風(fēng)險,投資需謹(jǐn)慎�����。

相關(guān)股票:

芯原股份、晶方科技��、長電科技����、通富微電、華天科技�����、華峰測控

投資要點:

? Chiplet帶來產(chǎn)業(yè)鏈環(huán)節(jié)顛覆式改變�����,設(shè)計彈性�、成本節(jié)省、加速上市等眾多優(yōu)點��。

? Chiplet新型設(shè)計技術(shù)的出現(xiàn)����,是國內(nèi)IC產(chǎn)業(yè)彎道超車的有利契機。

? 據(jù)Omdia報告���,預(yù)計2024年Chiplet市場規(guī)模會達(dá)到58億美元�����,2035年則超過570億美元�����。

正文部分

8月5日�,半導(dǎo)體板塊掀漲停潮,38只漲停���、另有14只股票漲幅超過10%�����。從細(xì)分來看,Chiplet概念最為搶眼����。那么,什么是Chiplet��?該技術(shù)的價值何在����?概念股有哪些���?

一、傳統(tǒng)IC產(chǎn)業(yè)的挑戰(zhàn)

隨著芯片工藝不斷演進��,硅的工藝發(fā)展趨近于其物理瓶頸���,晶體管再變小變得愈加困難����,摩爾定律放緩�,但是算力和存儲的需求爆發(fā),傳統(tǒng)方式推進芯片性能很難維持產(chǎn)業(yè)的持續(xù)發(fā)展����,行業(yè)進入后摩爾時代。

當(dāng)前IC技術(shù)瓶頸與業(yè)務(wù)需求的主要矛盾在于:

? 單位算力與數(shù)據(jù)量增速的矛盾:人工智能��、大數(shù)據(jù)����、5G 等技術(shù)發(fā)展,使數(shù)據(jù)量呈指數(shù)級增加�����,而單位算力的增速卻愈發(fā)遲緩。

? 性能和功耗比提升的矛盾:芯片性能的提升會伴隨著功耗的大幅增長�,從而導(dǎo)致應(yīng)用場景碎片化,無法攤薄芯片成本�。

? 研發(fā)成本和交付周期增加:隨著先進制程的進步,芯片制造成本與研發(fā)投入也大大增加�����。目前����,5nm芯片的研發(fā)費用已經(jīng)超過5億美元 ,3nm的研發(fā)費用預(yù)期將超過15億美元�����。

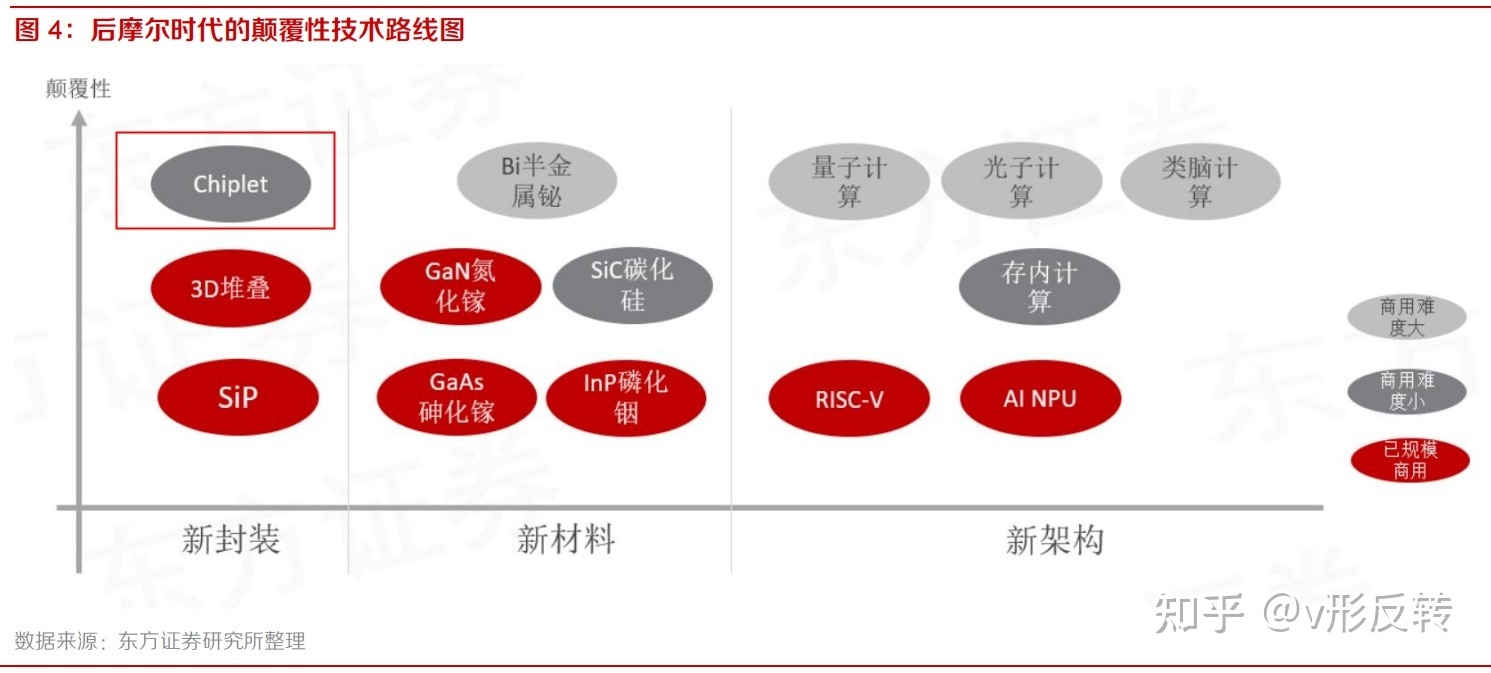

而從后摩爾時代創(chuàng)新的方式看��,主要圍繞新封裝��、新材料和新架構(gòu)三方面展開��,如下圖所示:

? 新封裝領(lǐng)域�,3D 封裝、SiP(System In a Package����,系統(tǒng)級封裝)已實現(xiàn)規(guī)模商用,以 SiP等先進封裝為基礎(chǔ)的 Chiplet 模式未來市場規(guī)模有望快速增長�����,目前臺積電����、AMD、Intel 等廠商已紛紛推出基于 Chiplet 的解決方案�����。

? 新材料領(lǐng)域����,隨著 5G、新能源汽車等產(chǎn)業(yè)的發(fā)展���,硅難以滿足對高頻����、高功率、高壓的需求以 GaAs����、GaN、SiC 為代表的第二代和第三代半導(dǎo)體迎來發(fā)展契機����。

? 新架構(gòu)領(lǐng)域,以 RISC-V 為代表的開放指令集將取代傳統(tǒng)芯片設(shè)計模式�,更高效應(yīng)對快速迭代、定制化與碎片化的芯片需求�。為應(yīng)對大數(shù)據(jù)、人工智能等高算力的應(yīng)用要求�,AI NPU 興起。存內(nèi)計算架構(gòu)將數(shù)據(jù)存儲單元和計算單元融合為一體��,能顯著減少數(shù)據(jù)搬運�,極大地提高計算并行度和能效。長期來看����,量子、光子�、類腦計算也有望取得突破。

?

二��、新封裝: Chiplet模式有望興起

Chiplet也稱“小芯片”或“芯?��!?�,它是一種功能電路塊�,包括可重復(fù)使用的IP塊(Intellectual Property Core���,是指芯片中具有獨立功能的電路模塊的成熟設(shè)計��,也可以理解為芯片設(shè)計的中間構(gòu)件)����。具體來說�����,該技術(shù)是將一個功能豐富且面積較大的芯片裸片(die)拆分成多個芯粒(chiplet)�����,這些預(yù)先生產(chǎn)好的����、能實現(xiàn)特定功能的芯粒組合在一起�,通過先進封裝的形式(比如3D封裝)被集成封裝在一起即可組成一個系統(tǒng)芯片��。(chiplet模式示例圖見下)

?

Chiplet 模式兼具設(shè)計彈性�、成本節(jié)省、加速上市等優(yōu)勢��,已被公認(rèn)為后摩爾時代半導(dǎo)體產(chǎn)業(yè)的最優(yōu)解集之一�����,在產(chǎn)業(yè)鏈上下游企業(yè)的共同推進下���,Chiplet已經(jīng)加速進入商業(yè)應(yīng)用����,應(yīng)用領(lǐng)域包括新一代移動通信����、高性能計算、自動駕駛以及物聯(lián)網(wǎng)等����。

?

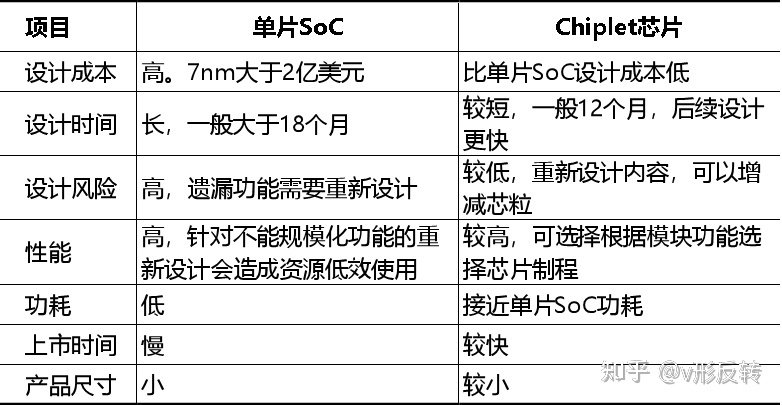

綜合而言,Chiplet具有如下優(yōu)勢(Soc與Chiplet的對比見下圖):

? 通過把大芯片分割成芯粒,可有效改善生產(chǎn)的良率�����,降低制造成本�。

? 模塊化設(shè)計思路可以提高芯片研發(fā)速度�����,降低研發(fā)成本����。也可以使用現(xiàn)有的成熟芯片降低開發(fā)和驗證成本。

? 可根據(jù)不同IP的需求��,選擇適合的工藝節(jié)點�。在芯片設(shè)計中,對于不同目的和類型的電路��,并不是最新的工藝就總是最合適的����。在目前的單硅片系統(tǒng)里,系統(tǒng)只能在一個工藝節(jié)點上實現(xiàn)��。而對于很多功能來說,使用成本高風(fēng)險大的最新工藝既沒有必要又非常困難��,比如一些專用加速功能和模擬設(shè)計���。在chiplet模式下���,做系統(tǒng)設(shè)計的時候則有了更多的選擇。對于追求性能極限的模塊�,比如高性能CPU,可以使用最新工藝�;而特殊的功能模塊,比如存儲器���,模擬接口和一些專用加速器����,則可以按照需求選擇性價比最高的方案�。

? 架構(gòu)設(shè)計的靈活性。以chiplet構(gòu)成的系統(tǒng)可以說是一個“超級”異構(gòu)系統(tǒng)��,給傳統(tǒng)的異構(gòu)SoC增加了新的維度����,至少包括空間維度和工藝選擇的維度。首先,先進的集成技術(shù)在3D空間的擴展可以極大提高芯片規(guī)模��;第二��,結(jié)合前述的工藝靈活性�����,可能在架構(gòu)設(shè)計中有更合理的功能/工藝的權(quán)衡��;第三�,系統(tǒng)的架構(gòu)設(shè)計�����,特別是功能模塊間的互聯(lián)�����,有更多優(yōu)化的空間�。

? 不同的芯粒可以使用不同的工藝節(jié)點制造�����,甚至可以有不同的供應(yīng)商提供。一些經(jīng)過驗證且技術(shù)成熟的芯??梢灾貜?fù)使用,這樣做既減少了企業(yè)的設(shè)計時間和成本�,還能有效擴充企業(yè)的資源庫。

?

三����、Chiplet的難點及發(fā)展趨勢

讓多個芯粒互聯(lián)起來并最終異構(gòu)集成成為一個大芯片�����,主要有兩個技術(shù)難點:

? 互聯(lián)��。如何讓芯粒之間高速互聯(lián)����,是Chiplet技術(shù)落地的關(guān)鍵。芯片設(shè)計公司在設(shè)計芯粒之間的互聯(lián)接口時��,首要保證的是高數(shù)據(jù)吞吐量�����,另外��,數(shù)據(jù)延遲和誤碼率也是關(guān)鍵要求,還要考慮能效和連接距離�。

? 封裝。怎么把多個Chiplet封裝起來���,而且解決好散熱問題:一是封裝體內(nèi)總熱功耗將顯著提升�;二是芯片采用2.5D/3D堆疊��,增加了垂直路徑熱阻��;三是更加復(fù)雜的SiP���,跨尺度與多物理場情況下熱管理設(shè)計復(fù)雜�。

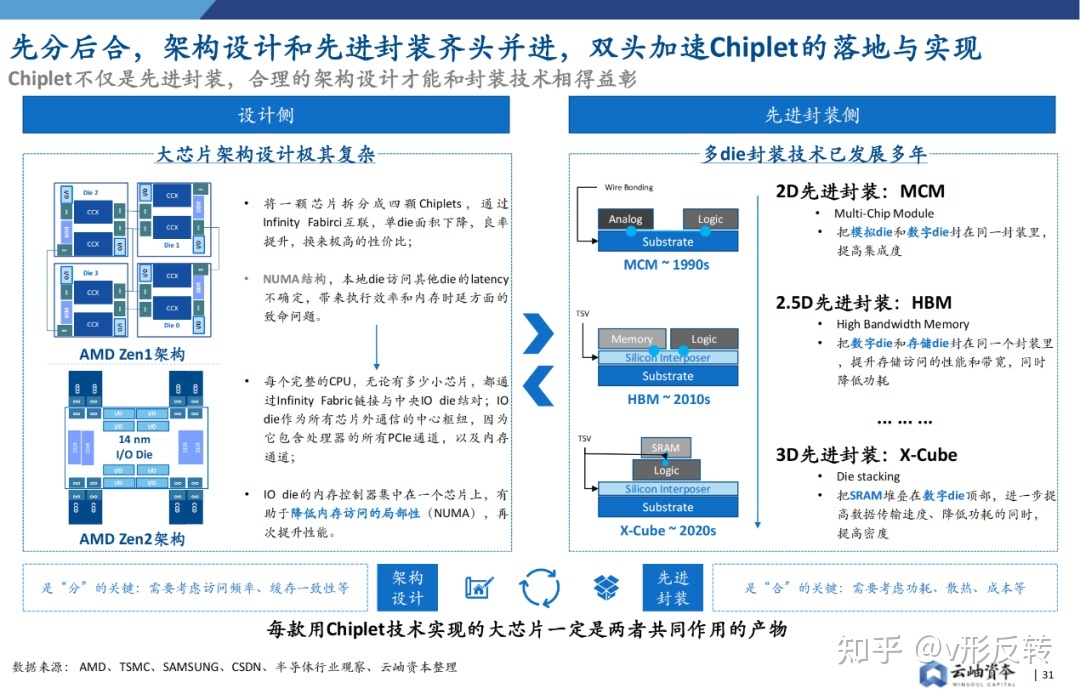

云岫資本的報告顯示���,目前臺積電、英特爾���、AMD等國際巨頭相繼布局 Chiplet�����,標(biāo)準(zhǔn)協(xié)議是其中的重要部分�。今年 UCIe 標(biāo)準(zhǔn)的推出對Chiplet行業(yè)起到了非常大的推動作用,各大廠商可以用同一個協(xié)議快速迭代�����。未來Chiplet 產(chǎn)業(yè)會逐漸成熟�,形成包括互聯(lián)接口、架構(gòu)設(shè)計����、制造和先進封裝的完整產(chǎn)業(yè)鏈,中國廠商面臨巨大發(fā)展機遇����。

?

據(jù)云岫資本判斷,短期內(nèi)�����,各Chiplet廠商會“各自為營”地通過自重用和自迭代利用這項技術(shù)的多項優(yōu)勢��,而在接口���、協(xié)議���、工藝都更加開放和成熟的未來�,產(chǎn)業(yè)鏈的各環(huán)節(jié)都將迎來換血����,“晶體管級復(fù)用”會成為現(xiàn)實。

?

四�、相關(guān)股票

? 芯原股份:公司將著力發(fā)展Chiplet業(yè)務(wù),以實現(xiàn)IP芯片化并進一步實現(xiàn)芯片平臺化����,為客戶提供更加完備的基于Chiplet的平臺化芯片定制解決方案。

? 長電科技:公司已加入UCle產(chǎn)業(yè)聯(lián)盟����,共同致力于Chiplet核心技術(shù)突破和成品創(chuàng)新發(fā)展,積極推動Chiplet接口規(guī)范標(biāo)準(zhǔn)化����。公司去年推出了XDFOI全系列極高密度扇出型封裝解決方案����,該技術(shù)是一種面向Chiplet的極高密度、多扇出型封裝高密度異構(gòu)集成解決方案��。

? 晶方科技���。晶圓級TSV是Chiplet技術(shù)路徑的一個重要部分�,晶方科技也在研究Chiplet技術(shù)路徑的走向。

? 通富微電:背靠AMD(chiplet首家商業(yè)化大規(guī)模生產(chǎn)的IC企業(yè))�,AMD占公司營收40%。公司在Chiplet��、2.5D��、3D堆疊等方面均有布局和儲備�����。

? 華天科技:掌握Chiplet相關(guān)技術(shù)�����。

? 華峰測控:chiplet需求增加的CP測試對測試機有帶動作用�。

參考研報或文章:

1. 云岫資本,《2022年中國半導(dǎo)體投資深度分析與展望》

2. 黃晶晶����,《中國大陸芯片IP TOP1公司,5nm設(shè)計項目流片���,發(fā)力Chiplet 業(yè)務(wù)》

3. 格隆匯���,《Chiplet能為芯片設(shè)計帶來哪些變革����?》

4. 架構(gòu)師技術(shù)聯(lián)盟�,《Chiplet如何革新半導(dǎo)體IP業(yè)務(wù)模式?》